The ChipFlow Configurator has launched

Designing a custom ASIC or system-on-chip involves a large amount of upfront work before development can even begin. Architecture definition, IP selection, bus connectivity, pin planning, and project setup all require careful coordination. The ChipFlow Configurator is a free, open source chip design configuration tool created to reduce this early-stage burden and make custom silicon projects easier to start and manage.

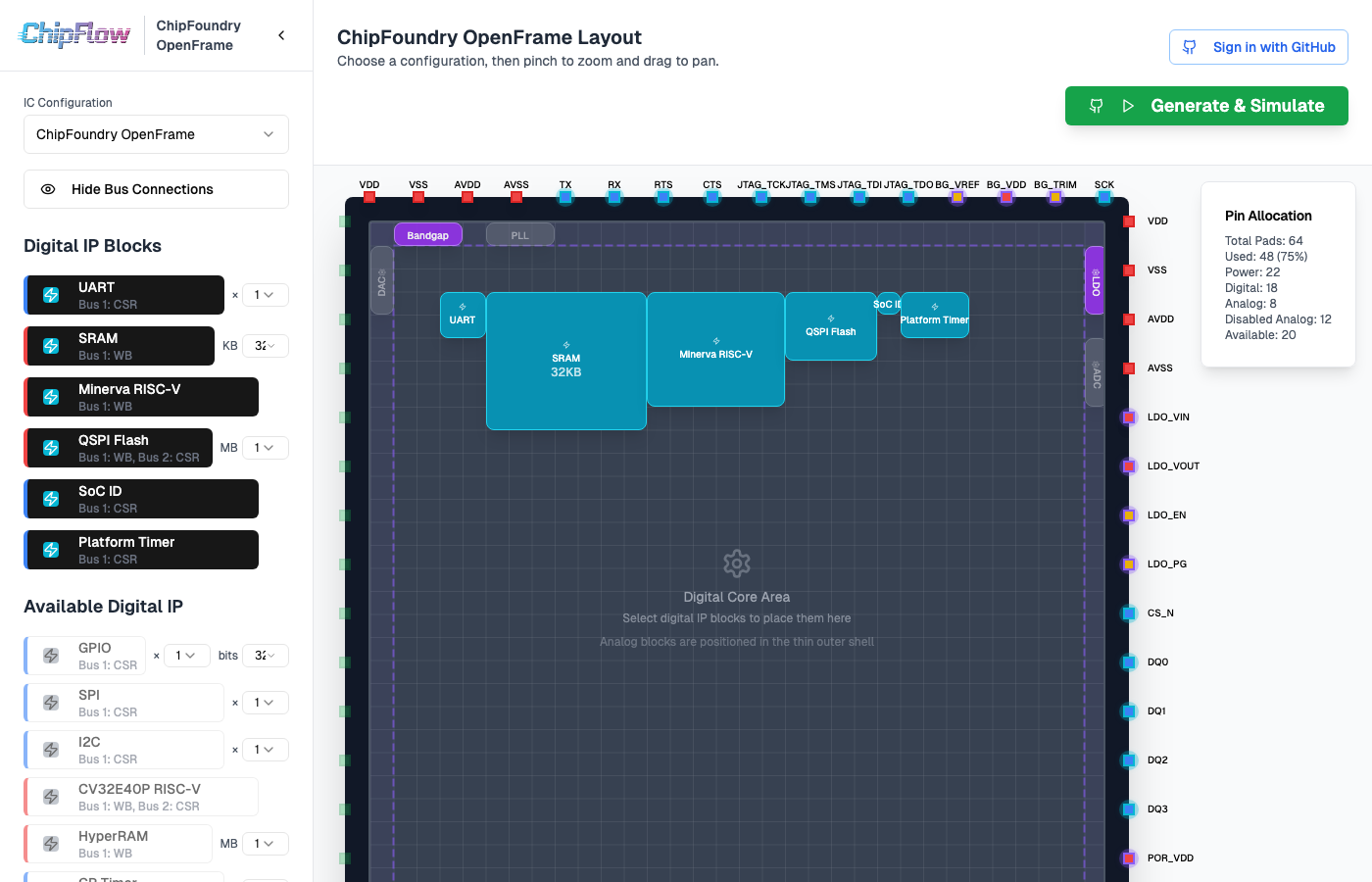

The Configurator is a browser-based ASIC and SoC architecture tool that allows engineers to define hardware systems visually. Users begin with proven open templates and configure their design by selecting processors, memories, peripherals, and interconnect IP blocks. The tool automatically handles connectivity, address maps, and pin assignments, helping teams avoid common integration mistakes and ensuring that architectural intent is captured clearly and consistently.

Once a design is complete, the ChipFlow Configurator generates a complete GitHub repository containing RTL, configuration files, and project structure needed to begin implementation. A ready-to-use development environment is created alongside the repository, removing the need for manual toolchain setup. This enables teams to move directly into simulation, firmware development, and iterative hardware design.

As a free and open source hardware design tool, the ChipFlow Configurator is intended to support engineers exploring custom ASICs, open source silicon, RISC-V systems, and application-specific SoCs. It removes much of the repetitive setup work associated with early chip development while remaining transparent and extensible for teams that need full control over their design.

By lowering the barrier to entry and automating early configuration steps, the ChipFlow Configurator provides a practical foundation for modern, collaborative chip development, helping teams move from concept to implementation with less risk and less overhead.